# MMDS TCM/QAM Demodulator + FEC + ADC

**Preliminary**

# Description

The CXD1958Q is an integrated TCM/QAM demodulator for MMDS systems using the DAVIC MMDS standard. This highly integrated device incorporates an internal 8-bit ADC, image rejection and root-raised cosine filters, all-digital symbol timing recovery PLL, adaptive decision feedback equalizer (DFE) with 10 feedforward and 30 feedback taps, 4-D TCM decoder, and DAVIC/DVB compliant forward error correction comprising (204,188) Reed Solomon decoder, a programmable de-interleaver with I = 12 and I = 204, and a de-randomiser. All internal clocks are generated from a single external 30MHz reference crystal.

Device functionality also includes 3-wire bus interface for configuring up to 2 tuner synthesizers, a sigma delta tuner IF-AGC output, a user programmable RF-AFC sigma delta output, spectrum inversion of the received signal for tuner compatibility, and a highly configurable MPEG2-TS interface. An I<sup>2</sup>C bus interface provides on-board configuration and status monitoring of various functions including access to the equalizer tap values and constellation points. JTAG provides boundary scan test compatibility.

## **Features**

- DAVIC MMDS V1.1 and V1.3 compliant

- Supports 16, 64 and 256QAM

- Supports 16, 64 and 256 TCM

- Internal 8-bit ADC

- Interface for 10-bit external ADC

- 36.125MHz nominal IF input

- Symbol rate range 5 5.304Mbaud in 6MHz channels

- Integrated matched filtering with 0.15 roll-off factor

- ±400KHz internal carrier offset compensation with negligible losses @ 5Mbaud 6MHz channel

- Symbol timing loop designed to acquire with large offsets. Negligible losses for ±100ppm offsets

- All internal clocks derived from single fixed frequency crystal (30MHz)

- Supports fast re-acquisition mode

- 6µs echo cancellation @ 5Mbaud

- Constellation points and equalizer tap values readable via I<sup>2</sup>C bus

- C/N estimation readable via I2C bus

- Low implementation loss for AWGN only:

0.5dB @ 64QAM (using internal 8-bit A/D);

0.3dB @ 256QAM (excluding A/D);

measured at BER of 3x10<sup>-4</sup> Pre R/S

- I = 12 and I = 204 de-interleaving

- Fast I2C bus compatible control interface

- Tuner IF-AGC output

- User programmable tuner RF-AGC output

- Dedicated 3-wire bus interface to configure up to 2 tuner synthesizers

- 3.3V CMOS technology

- Supports JTAG boundary scan

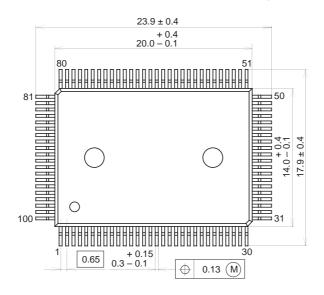

- 100-pin QFP package

## **Applications**

MMDS set-top boxes

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

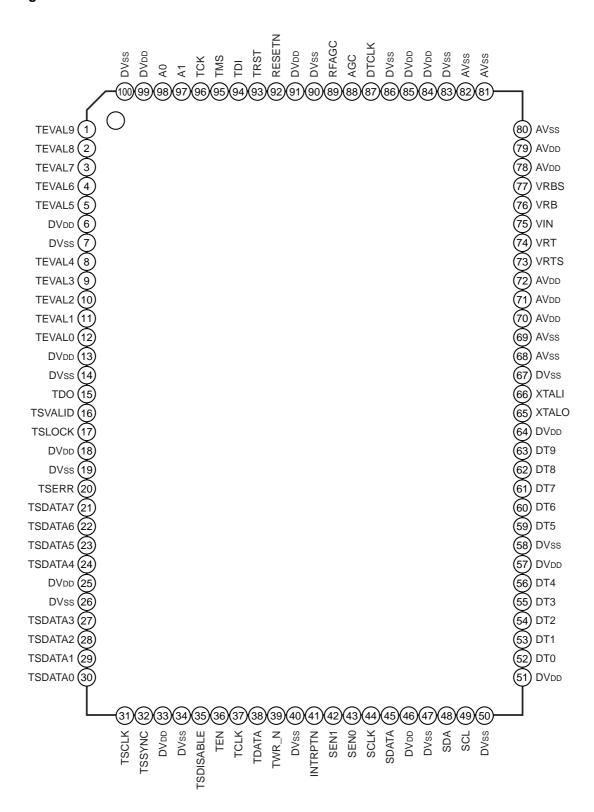

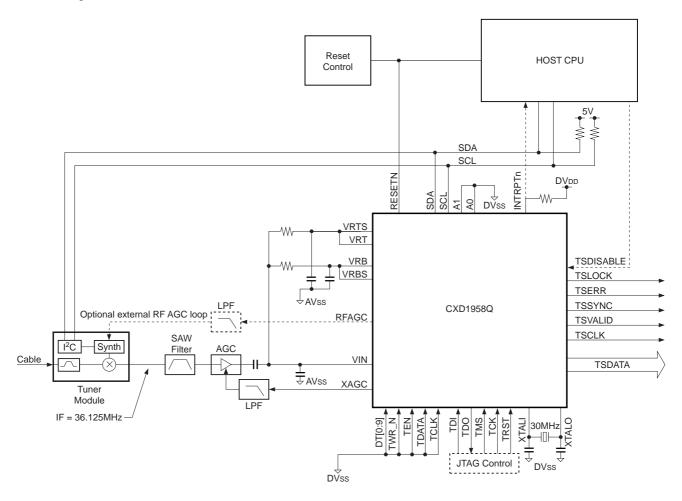

# **Pin Configuration**

Fig. 1. Pin Configuration

# **Pin Description**

# **Table 1. Pin Description**

| Name          | Pin No.                              | Туре                                            | Drive | Function                                                                                                                                                                                                                         |

|---------------|--------------------------------------|-------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Res | et                                   |                                                 |       |                                                                                                                                                                                                                                  |

| XTALO         | 65                                   | Crystal oscillator output                       | N/A   | Crystal oscillator cell output.                                                                                                                                                                                                  |

| XTALI         | 66                                   | Crystal oscillator input                        | N/A   | Crystal oscillator cell input.                                                                                                                                                                                                   |

| RESETN        | 92                                   | Digital<br>Schmitt-trigger<br>5V tolerant Input | N/A   | Active low hardware reset.                                                                                                                                                                                                       |

| ADC Interface |                                      |                                                 |       |                                                                                                                                                                                                                                  |

| VRTS          | 73                                   | Analog<br>output                                | N/A   | ADC internally generated top reference bias. This pin connects to VRT to self bias the top reference.                                                                                                                            |

| VRT           | 74                                   | Analog<br>input                                 | N/A   | ADC top reference voltage. Connects to VRTS for self bias.                                                                                                                                                                       |

| VIN           | 75                                   | Analog<br>input                                 | N/A   | Analog IF input.                                                                                                                                                                                                                 |

| VRB           | 76                                   | Analog<br>input                                 | N/A   | ADC bottom reference voltage.<br>Connects to VRBS for self bias.                                                                                                                                                                 |

| VRBS          | 77                                   | Analog<br>output                                | N/A   | ADC internally generated bottom reference bias. This pin connects to VRB to self bias the bottom reference.                                                                                                                      |

| MPEG2 Trans   | oort Stream I                        | nterface                                        |       |                                                                                                                                                                                                                                  |

| TSVALID       | 16                                   | Digital<br>tristate output                      | 4mA   | Identifies data portion of the MPEG2 transport stream packet (excludes parity bytes). The polarity and timing of this signal is programmable. Tristate following hardware reset. External pullup or pull-down resistor required. |

| TSLOCK        | 17                                   | Digital<br>output                               | 8mA   | MPEG2 transport stream lock indicator. The polarity of this signal is programmable.                                                                                                                                              |

| TSERR         | 20                                   | Digital<br>tristate output                      | 4mA   | MPEG2 transport stream error flag. Indicates uncorrectable errors in current packet. The polarity and timing of this signal is programmable. Tristate following hardware reset. External pullup or pull-down resistor required.  |

| TSDATA[7:0]   | 21, 22, 23,<br>24, 27, 28,<br>29, 30 | Digital<br>tristate output                      | 4mA   | MPEG2 transport stream parallel data output. Tristate following hardware reset. External pull-up or pull-down resistor required.                                                                                                 |

| Name           | Pin No.       | Туре                                            | Drive | Function                                                                                                                                                                                                                                                             |

|----------------|---------------|-------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPEG2 Trans    | port Stream   | Interface (Cont.)                               |       |                                                                                                                                                                                                                                                                      |

| TSCLK          | 31            | Digital<br>tristate output                      | 4mA   | MPEG2 transport stream byte clock. The polarity and timing of this signal is programmable. Tristate following hardware reset. External pull-up or pull-down resistor required.                                                                                       |

| TSSYNC         | 32            | Digital<br>tristate output                      | 4mA   | Indicates MPEG2 47H sync byte in transport stream packet. The polarity and timing of this signal is programmable. Tristate following hardware reset. External pull-up or pull-down resistor required.                                                                |

| TSDISABLE      | 35            | Digital<br>Schmitt-trigger<br>5V tolerant input | N/A   | Input to disable MPEG2-TS interface outputs.  MPEG2 transport stream output pins TSDATA[7:0], TSCLK, TSSYNC, TSVALID, TSERR to be put into tristate mode if this input is asserted high. The same outputs may also be set tristate via I <sup>2</sup> C bus control. |

| Tuner Interfac | ce (Control a | nd AGC)                                         |       |                                                                                                                                                                                                                                                                      |

| AGC            | 88            | Digital output                                  | 2mA   | External IF AGC control.                                                                                                                                                                                                                                             |

| RFAGC          | 89            | Digital output                                  | 2mA   | External RF AGC control.                                                                                                                                                                                                                                             |

| TEN            | 36            | Digital<br>Schmitt-trigger<br>5V tolerant input | N/A   | Host CPU control input. Can be used to control 3-wire bus outputs SEN0 and SEN1.                                                                                                                                                                                     |

| TCLK           | 37            | Digital<br>Schmitt-trigger<br>5V tolerant input | N/A   | Host CPU control input. Can be used to control 3-wire bus output SCLK.                                                                                                                                                                                               |

| TDATA          | 38            | Digital<br>Schmitt-trigger<br>5V tolerant input | N/A   | Host CPU control input. Can be used to control 3-wire bus output SDATA.                                                                                                                                                                                              |

| TWR_N          | 39            | Digital<br>Schmitt-trigger<br>5V tolerant input | N/A   | Host CPU control input used to register TEN, TCLK, TDATA on rising edge and update SEN, SCLK and SDATA outputs in one mode of the 3-wire bus operation.                                                                                                              |

| SEN1           | 42            | Digital open-drain output                       | 12mA  | 3-wire bus interface enable output. Polarity programmable and equivalent to polarity of SEN0. Must be pulled up by external resistor to 3.3V or 5V if used.                                                                                                          |

| SEN0           | 43            | Digital open-drain output                       | 12mA  | 3-wire bus interface enable output or pass-FET contol for tuner I <sup>2</sup> C bus. Programmable polarity. Must be pulled up by external resistor to 3.3V or 5V if used.                                                                                           |

| Name            | Pin No.                                         | Туре                                                                       | Drive                   | Function                                                                                         |

|-----------------|-------------------------------------------------|----------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| Tuner Interfac  | e (Control ar                                   | nd AGC) (Cont.)                                                            |                         |                                                                                                  |

| SCLK            | 44                                              | Digital open-drain output                                                  | 12mA                    | 3-wire bus interface clock output. Must be pulled up by external resistor to 3.3V or 5V if used. |

| SDATA           | 45                                              | Digital<br>open-drain output                                               | 12mA                    | 3-wire bus interface data output. Must be pulled up by external resistor to 3.3V or 5V if used.  |

| Host Control I  | nterface                                        |                                                                            |                         |                                                                                                  |

| SDA             | 48                                              | Digital bi-directional open-drain output Schmitt trigger 5V tolerant input | 3mA                     | I <sup>2</sup> C bus data. Must be pulled up by external resistor.                               |

| SCL             | 49                                              | Digital<br>Schmitt trigger<br>5V tolerant input                            | N/A                     | I <sup>2</sup> C bus clock. Must be pulled up by external resistor.                              |

| A1              | 97                                              | Digital<br>CMOS input                                                      | N/A                     | I <sup>2</sup> C bus address (variable part)                                                     |

| A0              | 98                                              | Digital<br>CMOS input                                                      | N/A                     | I <sup>2</sup> C bus address (variable part)                                                     |

| INTRPTN         | 41                                              | Digital<br>open-drain output                                               | 12mA                    | Programmable general interrupt pin.  Must be pulled up by external resistor to 3.3V or 5V.       |

| Testability and | d Evaluation                                    | Interface                                                                  |                         |                                                                                                  |

| DT[9:0]         | 63, 62, 61,<br>60, 59, 56,<br>55, 54, 53,<br>52 | Digital<br>bi-directional<br>tristate output<br>5V tolerant input          | IoL = 4mA<br>Ioн = -2mA | ADC digital bypass port for connection of an external ADC.                                       |

| DTCLK           | 87                                              | Digital output                                                             | 8mA                     | ADC clock for use with DT[9:0].                                                                  |

| TRST            | 93                                              | Digital input with pull-up                                                 | N/A                     | JTAG test reset input.                                                                           |

| TDO             | 15                                              | Digital<br>tristate output                                                 | 4mA                     | JTAG test data output.                                                                           |

| TDI             | 94                                              | Digital input with pull-up                                                 | N/A                     | JTAG test data input.                                                                            |

| TMS             | 95                                              | Digital input with pull-up                                                 | N/A                     | JTAG test mode select.                                                                           |

| тск             | 96                                              | Digital input                                                              | N/A                     | JTAG test clock.                                                                                 |

| TEVAL[9:0]      | 1, 2, 3, 4,<br>5, 8, 9, 10,<br>11, 12           | Digital<br>output                                                          | 4mA                     | Test data bus.                                                                                   |

| Name          | Pin No.                                                            | Туре   | Drive | Function                |

|---------------|--------------------------------------------------------------------|--------|-------|-------------------------|

| Power Supplie | es                                                                 |        |       |                         |

| DVpp          | 6, 13, 18,<br>25, 33, 46,<br>51, 57, 64,<br>84, 85, 91,<br>99      | Power  |       | Digital supply. (+3.3V) |

| DVss          | 7, 14, 19,<br>26, 34, 40,<br>47, 50, 58,<br>67, 83, 86,<br>90, 100 | Ground |       | Digital ground. (0V)    |

| AVss          | 68, 69, 80,<br>81, 82                                              | Ground |       | Analog ground. (0V)     |

| AVDD          | 70, 71, 72,<br>78, 79                                              | Power  |       | Analog supply. (+3.3V)  |

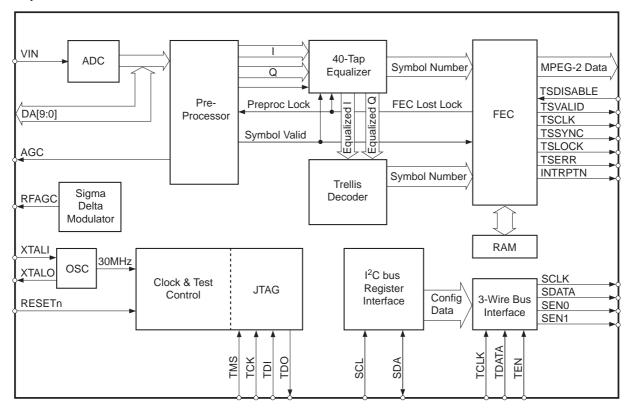

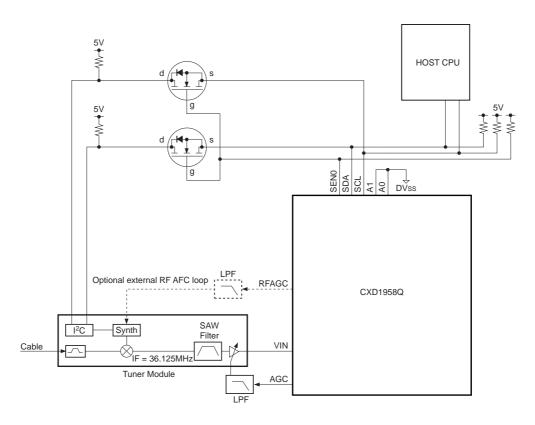

# **Description of Functions**

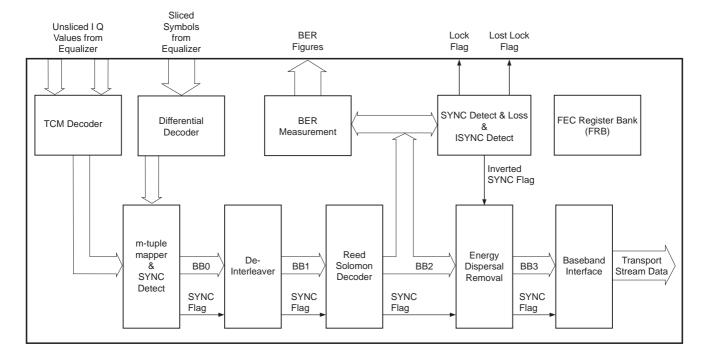

Fig. 2. Block Diagram

## 1. ADC

Input to the CXD1958Q is a single-ended IF signal centred at 36.125MHz. An integrated 8-bit ADC is clocked at 30MHz and used to directly band-pass sample the IF signal. The 8-bit ADC is self biased by connecting reference pins VRTS to VRT and reference pins VRBS to VRB. An option is provided to allow bypass of the internal ADC if an external converter up to 10 bits is desired.

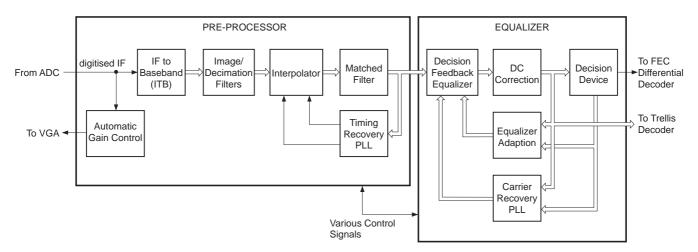

# 2. Pre-Processor and Equalizer

Fig. 3. Pre-Processor and Equalizer Block Diagram

#### 2-1. Automatic Gain Control - External

This block monitors the signal level at the output of the ADC and provides a pulse width-modulated control signal (IF-AGC) to drive an external (analog) variable gain amplifier (VGA). The polarity of this signal is I<sup>2</sup>C bus programmable. This circuit operates as an automatic gain control loop and is normally configured to maximize ADC dynamic range. Only a single external RC filter is required. It is possible to read the level being output on the IF-AGC signal via I<sup>2</sup>C bus to allow a separate RF-AGC sigma-delta output to be programmed for dual loop AGC systems.

### 2-2. IF to Baseband Conversion

The IF to Baseband block translates the received digitized IF signal to a complex baseband signal. Subsequent processing is performed in parallel on in-phase (I) and quadrature (Q) data paths.

#### 2-3. Decimation Filter

Sample rate conversion in the Decimation Filter block is used to optimize the operation of the timing loop over the symbol rate range.

## 2-4. Timing Recovery Loop

Symbol timing recovery is implemented using an all-digital PLL comprised of Interpolator, Matched Filter and Timing Recover PLL blocks in Fig. 3. This allows the sample rate to be unrelated to the symbol rate – sampling is asynchronous. The loop operates over the range (5 - 5.304) Mbaud with minimal performance degradation, surpassing the capability of an equivalent analog loop. The matched filter implements a square-root raised cosine function, matched to the equivalent transmitter filter for rejection of intersymbol interference (ISI).

# 2-5. Decision Feedback Equalizer

Adaptive equalization is performed using a Decision Feedback Equalizer implementation to remove echoes arising from channel multipath characteristics and any remaining ISI not removed by the matched filter in the pre-processor. The DFE filter structure has a feedforward (10 tap) and feedback (30 tap) section. The 30 tap feedback section removes post-cursive ISI up to 6ms delay which is sufficiently robust to remove long echoes in MMDS.

During acquisition of the QAM constellation, the adaptive equalizer steps through several modes of operation to achieve lock. The equalizer initially operates using a blind error signal to converge tap coefficients as no training sequence is provided in the QAM input data stream. The equalizer then switches to a decision-directed mode of operation where QAM data is used to generate the error signal to optimize convergence of tap coefficients.

An all-digital PLL is implemented for removal of carrier frequency and phase offsets.

## 2-6. DC Correction

Modulator carrier leakage appears as a DC component in the QAM constellation which must be removed before correct decisions can be made in Decision Device block. The DC Correction block completely removes this offset.

#### 2-7. Decision Device

The Decision Device block performs data slicing and symbol/bit mapping for 16, 64 and 256 QAM constellations. This block can also automatically or manually compensate for an inverted IF spectrum under I<sup>2</sup>C bus control. Modulation scheme recognition can be preset via I<sup>2</sup>C bus for fast acquisition.

# 2-8. Configuration and Control

Configuration and control is handled by a register bank accessible to an external processor over an I<sup>2</sup>C serial bus.

A pre-processor state machine controls the initial acquisition process until synchronisation is achieved. Once the pre-processor has acquired lock to the input symbol rate the equalizer section is enabled. Once enabled, Equalizer operation is also controlled by a state machine. Once Equalizer acquisition is achieved the condition is then maintained based upon acquisition and mode control information, supplied from the configuration registers, and MPEG Transport Stream status data from the FEC block.

#### 3. Post-Processor

Post-processing on the demodulated QAM/TCM signal implements the DAVIC MMDS standard. This includes differential decoding of the two most significant symbol bits (QAM mode only), mapping of decoded symbols onto bytes, Forney convolutional de-interleaving of the bytes (I = 12, and I = 204) to remove burst errors, Reed-Solomon (255, 239) error correction, MPEG-2 sync byte inversion and data stream de-randomization. Finally a baseband interface is included that provides an MPEG-2 compliant transport stream to the device output.

Fig. 4. Post-Processor Block Diagram

#### 3-1. Differential Decoder

In QAM mode, this decodes the MSB of the received QAM signal according to the equations given in the DAVIC MMDS standard. In TCM mode, the differential decoding is performed by the TCM decoder block.

### 3-2. TCM Decoder

The TCM decoder reduces the signal power required for robust reception in difficult channels whenever trellis coded modulation is used at the transmitter. TCM mode is selected by an I<sup>2</sup>C bus register bit. The TCM decoder block takes the equalized I/Q symbols as input data, and provides 7-bit (16-TCM), 11-bit (64-TCM), and 15-bit (256-TCM) outputs for each TCM symbol. Two I/Q pairs are required for each TCM symbol. The TCM block performs an internal synchronization sequence to ensure that the correct pair of QAM symbols is selected. There are several I<sup>2</sup>C bus registers to allow user configuration and monitoring of the synchronization sequence.

# 3-3. Symbol to Byte Mapper

The postprocessor maps differentially decoded symbols to bytes. The byte boundaries are determined by correlating the input symbols with the expected locations of the sync bytes. The number of consecutive successful correlations is compared against a threshold (SYNC\_LADDER\_LENGTH), and the symbol stream is flagged as locked when that threshold is achieved.

#### 3-4. De-interleaver and Reed Solomon Error Correction

DAVIC compatible forney type convolutional de-interleavering (I = 12, N = 204, M = 17) or (I = 204, N = 204, M = 1), where M = N/I) is applied to the bytes. I = 12 is used for 16/64 QAM/TCM modes. Either I = 12 or I = 204 can be programmed for 256 QAM/TCM modes. The resulting byte stream is corrected by a standard DAVIC/DVB (204, 188) Reed Solomon decoder (GF generation polynomial p (x) =  $x^8 + x^4 + x^3 + x^2 + 1$ ) which can correct up to 8 erroneous bytes per MPEG2 packet.

# 3-5. Sync Detection and Sync Loss

After R/S correction, the byte stream is checked for the occurrence of n MPEG-2 sync bytes, where n is programmable from 2 to 7 via an I<sup>2</sup>C bus register. This sync byte detection is used to indicate transport stream lock by activation of the TSLOCK pin. There are two methods used to indicate loss of Transport Stream Lock, selectable by an I<sup>2</sup>C bus register. One method indicates loss of lock immediately a sync byte is lost. The other method decrements the sync byte counter down by 1 from n, and only indicates loss of lock when the counter reaches zero, thus providing a filtering capability to allow easier sync locking.

# 3-6. Energy Dispersal De-randomiser

The error-corrected bytes are de-randomized with a 15-stage PRBS (Pseudo Random Binary Sequence) generator, with polynomial  $1 + X^{14} + X^{15}$  and start-up sequence "100101010000000". Sync bytes are not descrambled, and when an inverted sync byte is detected, every 8th packet, the PRBS resets to the start-up sequence and the sync byte is re-inverted. The de-scrambled data is output through the TSDATA pins, along with a data clock and synchronization signal.

#### 3-7. BER Calculation

In addition to the above functionality, the postprocessor includes comprehensive signal quality measurement logic. The Bit Error Rate (BER) of the received signal (before and after R/S correction) and a measure of the long-term signal quality are available via  $I^2C$  bus registers. The calculated Bit Error Rate (BER) of the received signal is accurate for pre R/S BER figures better than  $1 \times 10^{-3}$ .

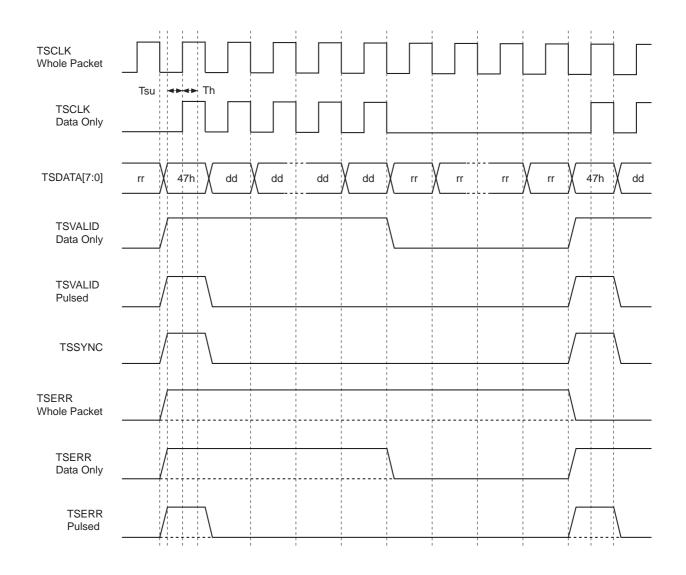

#### 3-8. MPEG2 Baseband Interface

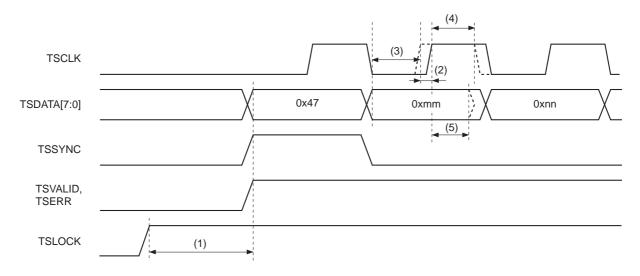

Fig. 5 illustrates the relationship between the CXD1958Q MPEG2 transport stream interface signals. The transport stream clock (TSCLK) can be programmed for the external device to sample on the rising or falling edge (only rising edge sampling is shown here). The interface supports a number of additional signals, which indicate the integrity of the output data. Once the demodulator has achieved lock to the MPEG2 sync byte, the transport stream interface is activated. Fig. 5 shows a complete MPEG2 packet consisting of a sync byte (47h) data bytes (dd) and Reed Solomon bytes (rr). Note that all the interface control signals have individual programmable polarity; active high signals are shown in the diagram.

**TSCLK** has two operating modes selected via I<sup>2</sup>C bus:

- Whole Packet Mode, where the clock is activated for all 204 bytes of the packet, requiring the external interface to use TSVALID to distinguish between data and 16 Reed Solomon bytes.

- Data Only Mode, where the clock is activated only for each of the 188 sync and data bytes, and remains inactive during the 16 Reed Solomon bytes.

**TSDATA[7:0]** is the byte wide MPEG2-TS data with programmable MSB/LSB ordering. The default is TSDATA7 being the MSB.

**TSVALID** has two operating modes selected via I<sup>2</sup>C bus:

- Data Only Mode: where TSVALID is set active during the 188 byte data portion of the packet, and reset inactive during the 16 Reed Solomon bytes. It is used by the external device as a clock enable to qualify when data is valid on TSDATA[7:0].

- Pulsed Mode: where TSVALID is set active during the MPEG2 sync byte and reset inactive for the remainder of the packet, and thus becomes equivalent to a sync byte indicator.

**TSSYNC** is set active during the MPEG2 sync byte and reset inactive for the remainder of the packet.

**TSERR** is only set active if the Transport Stream Error flag is set. This signal indicates that the Reed Solomon decoder was unable to correct all errors in the packet. There are 3 programmable modes for this signal:

- Whole Packet Mode: Active during the entire 204-byte packet

- Data Only Mode: Active during the 188 byte data portion of packet and inactive during the 16 Reed Solomon bytes

- Pulsed Mode: Pulsed active during sync byte period only

Fig. 5. MPEG2 Transport Stream Output Configurations

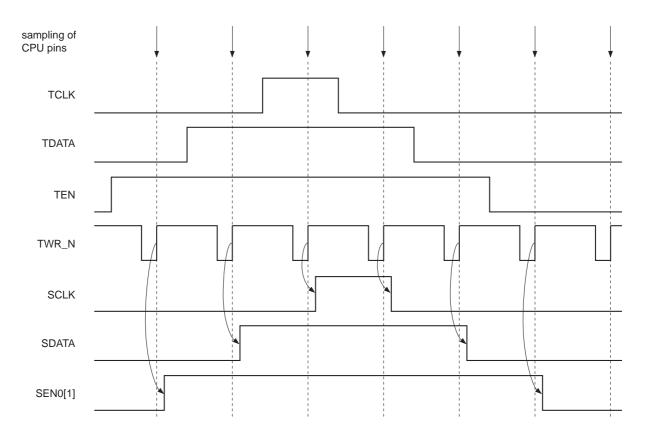

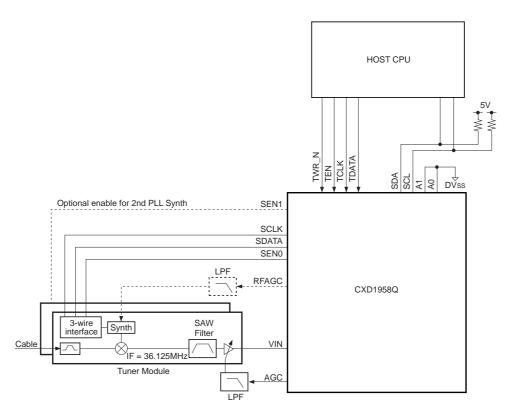

# 4. Tuner 3-Wire Bus Interface

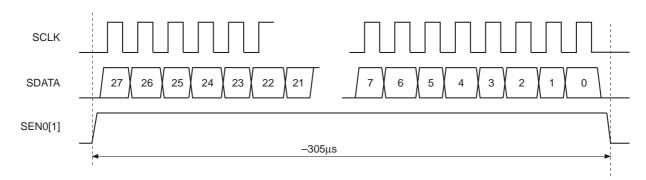

The interface allows two tuner synthesizers to be configured through the use of separate SEN0 and SEN1 enable output signals. The polarity of SEN0 and SEN1 can be programmed both active high or both active low by the SEN\_POL I<sup>2</sup>C bus register bit. There are two operating modes selected by I<sup>2</sup>C bus.

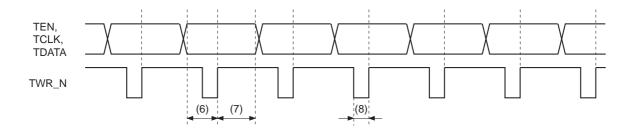

• Mode 0: The host CPU drives the 3-wire bus pins via the CPU interface pins TCLK, TDATA and TEN. These pins are connected to the CPU data bus and a decoded active low strobe is connected to the TWR\_N input pin. On each rising edge of TWR\_N, the data on TCLK, TDATA, and TEN is registered by the CXD1958Q demodulator, and driven out on the SCLK, SDATA and SEN0 or SEN1 pins respectively. The I<sup>2</sup>C bus register bit SEL selects whether SEN0 or SEN1 is activated during this transfer. Thus the transfer rate on the 3-wire bus interface in this mode is determined by the rate of CPU accesses. The operation of this mode is shown in Fig. 6.

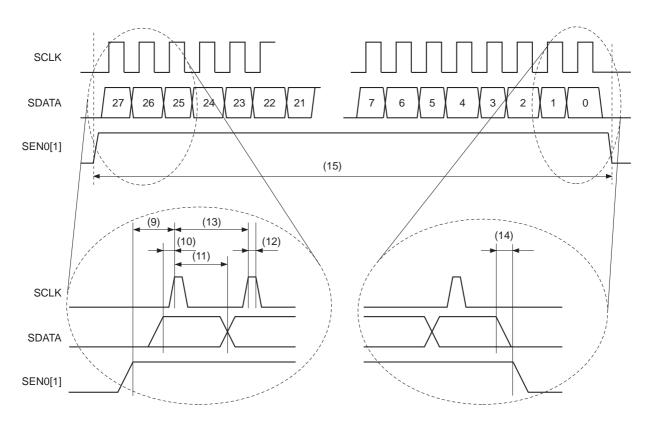

• Mode 1 :The CPU loads 4 I<sup>2</sup>C bus registers inside the TCM demodulator with 28 bits of data. The CPU selects which SEN0 or SEN1 output should be used by programming the I<sup>2</sup>C bus register bit (SEL), and then commands (by setting an I<sup>2</sup>C bus register bit SEND) the 3-wire bus state machine to transmit these 28 bits out of the 3-wire interface as shown in Fig. 7. When the transmission is complete, the I<sup>2</sup>C bus register bit (SEND) is reset to zero by the 3-wire bus state machine. This allows the CPU to poll the SEND bit to determine when it is able to write further data to the 3 I<sup>2</sup>C bus registers if it is necessary to send more data. The rate of transmission is fixed at 10.67µs per bit when using a 30MHz crystal oscillator on the CXD1958Q demodulator IC. The bit ordering of transmission starts with bit 27.

Fig. 6. 3-Wire Bus: Mode 0 Operation

Fig. 7. 3-Wire Bus: Mode 1 Operation

# 5. I<sup>2</sup>C Bus Interface

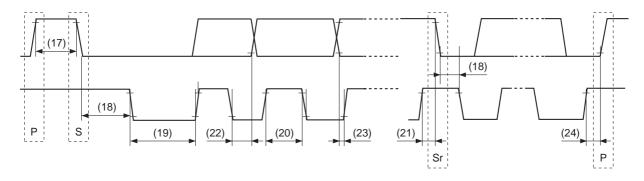

The CXD1958Q includes an  $I^2C$  bus compatible host interface, to enable access to the internal control registers. This supports accesses via an offset register at bit rates of up to 400Kbit/s. The 7-bit slave address for this device is [0, 0, 1, 1, 1, A1, A0], where A1 and A0 are set externally via device pins.

A summary of the CXD1958Q internal register set which can be accessed via  $I^2C$  bus is defined in Table 2. A full description of the registers is presented in "Control Register Definitions".

Table 2. I<sup>2</sup>C bus Interface Registers

| Sub-      | Nama             | R/W  | Width | Description                               | Value | on reset of typ | е    |

|-----------|------------------|------|-------|-------------------------------------------|-------|-----------------|------|

| address   | Name             | R/VV | bytes | Description                               | H/W   | Cold            | Warm |

| 0         | CHIP_INFO        | R    | 1     | Device<br>version/revision<br>information | 20h   | 20h             | 20h  |

| 1         | RST_REG          | RW   | 1     | Device reset register                     | F4h   | F4h             | F1h  |

| 2         | INTERRUPT_SOURCE | RW   | 1     | Interrupt source register                 | 0     | 0               |      |

| 3         | TSMSTATUS        | R    | 1     | Pre-processor status                      | 0     | 0               | _    |

| 4         | ESMSTATUS        | R    | 1     | Equalizer status                          | 01h   | 01h             | _    |

| 5         | FEC_STATUS       | R    | 1     | FEC status                                | 10h   | 10h             | _    |

| 6         | QAMCONFIG        | RW   | 1     | QAM level configuration                   | 84h   | 84h             | _    |

| 7         | CARRIEROFFSET    | R    | 1     | Detected frequency offset                 | 0     | 0               | _    |

| 8         | DETECTEDQAM      | R    | 1     | Detected QAM<br>level                     | 0     | 0               | _    |

| 9 – 0AH   | DETECTEDSYMRATE  | R    | 2     | Symbol rate at which locked               | 0     | 0               | _    |

| 0BH – 0DH | BER_EST          | R    | 3     | Bit Error Rate estimate                   | 0     | 0               | _    |

| 0EH – 0FH | CWRJCT_CNT       | R    | 2     | Codeword reject count                     | 0     | 0               | _    |

| 10H       | INTERRUPT_MASK   | RW   | 1     | Interrupt mask register                   | 0     | 0               | _    |

| 11H       | PRECONFIG        | RW   | 1     | Pre-processor configuration               | 89h   | 89h             | _    |

| 12H       | AGCCTRL          | RW   | 1     | External AGC control                      | 0     | _               | _    |

| 13H       | EQUCONFIG        | RW   | 1     | Equalizer configuration                   | 03h   | 03h             |      |

| Sub-      | Name              | R/W    | Width | Description                                   | Value              | on reset of typ    | е    |

|-----------|-------------------|--------|-------|-----------------------------------------------|--------------------|--------------------|------|

| address   | inallie           | IX/ VV | bytes | Description                                   | H/W                | Cold               | Warm |

| 14H       | FEC_PARAMS        | RW     | 1     | FEC configuration                             | 32h                | _                  | _    |

| 15H – 16H | SYMRATETRIAL0     | RW     | 2     | Symbol rate table entry                       | 0AABh<br>5Msym/s   | 0AABh<br>5Msym/s   | _    |

| 17H – 18H | SYMRATETRIAL1     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 19H – 1AH | SYMRATETRIAL2     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 1BH – 1CH | SYMRATETRIAL3     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 1DH – 1EH | SYMRATETRIAL4     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 1FH – 20H | SYMRATETRIAL5     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 21H – 22H | SYMRATETRIAL6     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 23H – 24H | SYMRATETRIAL7     | RW     | 2     | Symbol rate table entry                       | 0                  | 0                  | _    |

| 25H       | SET_SYNC_DETECT   | RW     | 1     | FEC sync detect thresholds                    | 1Dh                | 1Dh                | _    |

| 26H       | LT_QLTY_THRESHOLD | RW     | 1     | Long term quality threshold                   | 04h                | 04h                | _    |

| 27H       | BER_EST_PERIOD    | RW     | 1     | Bit error rate<br>measurement<br>period       | 0Eh                | 0Eh                | _    |

| 28H       | ADC_CAL_PERIOD    | RW     | 1     | Not used in this application                  | FFh                | FFh                | _    |

| 29H – 2AH | ITBFREQ           | RW     | 2     | Nominal frequency of receive local oscillator | 32EFh<br>36.125MHz | 32EFh<br>36.125MHz | _    |

| 2BH       | EQUTAPSELECT      | RW     | 1     | Equalizer tap address number                  | 0                  | 0                  | _    |

| 2CH       | EQUTAPI           | R      | 1     | In-phase<br>component of<br>equalizer tap     | 0                  | 0                  | _    |

| 2DH       | EQUTAPQ           | R      | 1     | Quadrature<br>component<br>equalizer tap      | 0                  | 0                  | _    |

| 2EH       | CONSTELLATIONI    | R      | 1     | In-phase equalizer output                     | 0                  | 0                  | _    |

| 2FH       | CONSTELLATIONQ    | R      | 1     | Quadrature-phase equalizer output             | 0                  | 0                  | _    |

| Sub-      | Name        | R/W  | Width | Description                                             | Value | on reset of typ | е    |

|-----------|-------------|------|-------|---------------------------------------------------------|-------|-----------------|------|

| address   | Name        | K/VV | bytes | Description                                             | H/W   | Cold            | Warm |

| 30H – 31H | AGCIFINTG   | R    | 2     | IF external gain control integrator output level        | 0     | 0               | _    |

| 32H – 33H | RFAGC       | RW   | 2     | RF gain control                                         | 0     | 0               | _    |

| 34H – 37H | TUNER_CTRL  | RW   | 4     | Tuner interface control I/F                             | 0h    | 0h              | _    |

| 38H       | TCM_CONFIG  | RW   | 1     | TCM configuration and synchronization control           | ABh   | ABh             | _    |

| 39H       | TS_MODE     | RW   | 1     | Transport stream output control                         | B4h   | B4h             | _    |

| ЗАН       | SNRESTIMATE | R    | 1     | Estimate of SNR in channel                              | 0     | 0               | _    |

| 3ВН       | LMSMUTRACK  | RW   | 1     | Equalizer adaption constant                             | 03h   | 03h             | _    |

| зСН       | SWEEPRNG    | RW   | 1     | Maximum<br>frequency offset<br>carrier loop<br>acquires | 80h   | 80h             | _    |

| 83H       | AGCTGT      | RW   | 1     | External gain control target signal level               | 69h   | 69h             | _    |

# 6. JTAG Test Interface

A JTAG test interface is provided using the pins TDI, TDO, TMS, TRST and TCK. The Interface conforms to the IEEE1149.1 standard and provides access to the device boundary scan chain.

# **Electrical Characteristics**

# 1. Absolute Maximum Ratings

$(Ta = 25^{\circ}C, AVss = 0V, DVss = 0V)$

| Item                                    | Symbol | Condition                                                                                                                 | Min.            | Max.                   | Unit |

|-----------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|------|

| Digital power supply                    | DVDD   |                                                                                                                           | DVss - 0.5      | +4.6                   | V    |

| Analog power supply                     | AVDD   |                                                                                                                           | AVss - 0.5      | +4.6                   | V    |

| Input voltage: -3.3V only input pins    |        | Pins TRST, TDI, TMS, TCK, A1, A0, VRT, VIN, VRB, XTALI                                                                    | DVss - 0.5      | DV <sub>DD</sub> + 0.5 |      |

| Input voltage: -5V tolerant input pins  | Vı     | Pins SCL, SDA, RESETN, TEN,<br>TCLK, TDATA, TWR_N,<br>TSDISABLE, DT[9:0]                                                  | DVss - 0.5      | DVss + 5.5             | V    |

| Output voltage: -3.3V only pins         | Vo     | Pins TEVAL[9:0], TDO, TVALID,<br>TSLOCK, TSERR, TSDATA[7:0],<br>TSCLK, TSSYNC, XTALO,<br>DTCLK, AGC, RFAGC, VRTS,<br>VRBS | DVss - 0.5      | DVpd + 0.5             | V    |

| Output voltage: -5V tolerant input pins |        | Pins INTRPTN, SEN0, SEN1,<br>SCLK, SDATA, SDA, DT[9:0]                                                                    | DVss - 0.5      | DVss + 5.5             |      |

| Storage temperature                     | Тѕтс   |                                                                                                                           | <del>-</del> 55 | +150                   | °C   |

#### Notes:

- 1. The device must be operated within the limits of the absolute maximum ratings. If the device is operated outside these conditions, the device may be permanently damaged.

- 2. Functional operation at or outside any of the conditions indicated in the absolute maximum ratings is not implied.

- 3. Exposure of the device to the absolute maximum rating condition for extended periods can affect system reliability.

- 4. 5V tolerant inputs and outputs are only 5V tolerant while the device power is applied. If no device power is applied there in no protection to 5V levels and the device may be permanently damaged. It is important to observe the conditions for 5V protection when sequencing power supplies in the application.

# 2. Recommended Operating Conditions

| Item                         | Symbol | Condition | Min. | Тур. | Max. | Unit |

|------------------------------|--------|-----------|------|------|------|------|

| Digital power supply         | DVDD   | DVss = 0V | 3.0  | 3.3  | 3.6  | V    |

| Analog power supply          | AVDD   | AVss = 0V | 3.0  | 3.3  | 3.6  | V    |

| Crystal oscillator frequency | fxtal  |           | 30   |      | 30   | MHz  |

| Ambient temperature range    | Та     |           | 0    |      | +70  | °C   |

# 3. DC Electrical Characteristics

$0^{\circ}\text{C} < \text{Ta} < 70^{\circ}\text{C}$ , DVss = AVss = 0V, 3.0V < DVpp, AVpp < 3.6V

| Item                         | Symbol | Condition                                                                                                                                                                                                         | Min.                   | Тур.     | Max.    | Unit |

|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|---------|------|

| Input low voltage            | VIL    | Except pins SCL, SDA                                                                                                                                                                                              |                        |          | 0.2DVDD | V    |

| Input low voltage            | VIL    | Pins SCL, SDA                                                                                                                                                                                                     |                        |          | 0.3DVDD | V    |

| Input high voltage           | ViH    |                                                                                                                                                                                                                   | 0.7DV <sub>DD</sub>    |          |         | V    |

| Input voltage hysteresis     | VHYST  | Pins RESETN, TSDISABLE,<br>TEN, TCLK, TDATA, TWR_N,<br>SDA, SCL                                                                                                                                                   |                        | 0.5      |         | V    |

| Input low current            | lıL    | Vin = DVss, pins TCK, A1, A0                                                                                                                                                                                      | -10                    |          |         | μΑ   |

| Input low current            | lıL    | Vin = DVss, pins TMS, TDI,<br>TRST                                                                                                                                                                                | -240                   | -100     | -40     | μΑ   |

| Input low current            | lı∟    | Vin = DVss, pins SCL, SDA,<br>RESETN, TEN, TCLK, TDATA,<br>TWR_N, TSDISABLE, DT[9:0]                                                                                                                              | -40                    |          |         | μA   |

| Input high current           | Іін    | Vin = DV <sub>DD</sub> , pins TRST, TDI,<br>TMS, TCK, A1, A0                                                                                                                                                      |                        |          | +10     | μA   |

| Input high current           | Іін    | Vin = 5.5V, pins SCL, SDA,<br>RESETN, TEN, TCLK, TDATA,<br>TWR_N, TSDISABLE, DT[9:0]                                                                                                                              |                        |          | +40     | μA   |

| Output voltage LOW           | Vol    | IoL = 2mA, pins AGC, RFAGC IoL = 3mA, pin SDA IoL = 4mA, pins TSVALID, TSERR, TDATA[7:0], TSCLK, TSSYNC, DT[9:0], TDO, TEVAL[9:0] IoL = 8mA, pins TSLOCK, DTCLK IoL = 12mA, pins SEN0, SEN1, SCLK, SDATA, INTRPTN |                        |          | 0.4     | V    |

| Output voltage HIGH          | Vон    | IOH = -2mA, pins AGC, RFAGC,<br>DT[9:0]<br>IOH = -4mA, pins TSVALID,<br>TSERR, TDATA[7:0], TSCLK,<br>TSSYNC, TDO, TEVAL[9:0]<br>IOH = -8mA, pins TSLOCK,<br>DTCLK                                                 | DV <sub>DD</sub> - 0.4 |          |         | V    |

| Output voltage HIGH          | Vон    | Iон = −2mA, pins DT[9:0]                                                                                                                                                                                          | 2.4                    |          |         | V    |

| ADC bottom reference voltage | VRB    | VRT connected to VRTS and VRB connected to VRBS                                                                                                                                                                   |                        | 0.33DVpd |         | V    |

| ADC top reference voltage    | VRT    | VRT connected to VRTS and VRB connected to VRBS                                                                                                                                                                   |                        | 0.66DVDD |         | V    |

| ADC input dynamic range      | VIADC  |                                                                                                                                                                                                                   |                        | 0.33DVpd |         | V    |

| Supply current               | IDD    | Total current AVDD + DVDD                                                                                                                                                                                         |                        | 330      |         | mA   |

# 4. AC Electrical Characteristics

# 4-1. Transport Stream Interface

Fig. 8. Transport Stream AC Timing

**Table 3. Transport Stream AC Timing Parameters**

$0^{\circ}\text{C} < \text{Ta} < 70^{\circ}\text{C}$ , DVss = AVss = 0V, 3.0V < DVpp, AVpp < 3.6V

| Timing parameter | Description                                                                                      | Min.      | Тур.  | Max.      | Unit |

|------------------|--------------------------------------------------------------------------------------------------|-----------|-------|-----------|------|

|                  | txtal,<br>Clock period defined by crystal oscillator                                             |           | 33.33 |           | ns   |

| 1                | ttslocksu,<br>TSLOCK valid setup time to TSSYNC, TSVALID<br>and TSERR                            | 3 × txtal |       |           | ns   |

| 2                | tтsлт,<br>transport stream clock jitter                                                          |           |       | txtal     | ns   |

| 3                | trssu,<br>transport stream TSDATA, TSSYNC, TSVALID<br>and TSERR setup time to TSCLK active edge  | 2 × txtal |       |           | ns   |

| 4                | ttshd,<br>transport stream TSDATA, TSSYNC, TSVALID<br>and TSERR hold time from TSCLK active edge |           |       | 2 × txtal | ns   |

| 5                | tтspw,<br>transport stream TSCLK pulse width                                                     | 2 × txtal |       |           | ns   |

# 4-2. Tuner 3-Wire Bus Interface

Fig. 9. Tuner 3-Wire Bus Mode 0 AC Timing

Table 4. Tuner 3-Wire Bus Mode 0 AC Timing Parameters

$0^{\circ}\text{C} < \text{Ta} < 70^{\circ}\text{C}$ , DVss = AVss = 0V, 3.0V < DVpd, AVpd < 3.6V

| Timing parameter | Description                                                                   | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------------------------------------------------------|------|------|------|------|

| 6                | thcpusu,<br>host CPU TEN, TCLK, and TDATA setup time<br>to TWR_N rising edge  |      |      | 40   | ns   |

| 7                | thcpuhd,<br>host CPU TEN, TCLK, and TDATA hold time<br>from TWR_N rising edge | 10   |      |      | ns   |

| 8                | thcpupw,<br>host CPU TWR_N pulse width                                        | 40   |      |      | ns   |

Fig. 10. Tuner 3-Wire Bus Mode 1 AC Timing

# Table 5. Tuner 3-Wire Bus Mode 1 AC Timing Parameters

$0^{\circ}\text{C} < \text{Ta} < 70^{\circ}\text{C}$ , DVss = AVss = 0V, 3.0V < DVpd, AVpd < 3.6V

| Timing parameter | Description                                                            | Min. | Тур.         | Max. | Unit |

|------------------|------------------------------------------------------------------------|------|--------------|------|------|

|                  | txtal, clock period defined by crystal oscillator                      |      | 33.33        |      | ns   |

| 9                | tsensu, 3-wire bus SEN0 or SEN1 active setup time to SCLK rising edge  |      | 192 × txtal  |      | ns   |

| 10               | tsdatasu,<br>3-wire bus SDATA setup time to SCLK rising<br>edge        |      | 64 × txtal   |      | ns   |

| 11               | tsdatahd,<br>3-wire bus SDATA hold time from SCLK rising<br>edge       |      | 256 × txtal  |      | ns   |

| 12               | tsclkpw, 3-wire bus SCLK high pulse width                              |      | 64 × txtal   |      | ns   |

| 13               | tsclkper,<br>3-wire bus SCLK period                                    |      | 320 × txtal  |      | ns   |

| 14               | tsenhd, 3-wire bus SEN0 or SEN1 hold time active after final SDATA bit |      | 64 × txtal   |      | ns   |

| 15               | tsenpw, 3-wire bus SEN0 or SEN1 active pulse width                     |      | 9152 × txtal |      | ns   |

# 4-3. I<sup>2</sup>C Interface

Fig. 11. I<sup>2</sup>C Interface AC timing

# Table 6. I<sup>2</sup>C Interface AC timing parameters

$0^{\circ}\text{C} < \text{Ta} < 70^{\circ}\text{C}$ , DVss = AVss = 0V, 3.0V < DVpp, AVpp < 3.6V

| Timing parameter | Description                                                                                                | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 16               | fscL,<br>SCL clock frequency                                                                               | 0    |      | 400  | kHz  |

| 17               | tsdabuf, Bus free time between a STOP (P) and START (S) condition                                          | 1.3  |      |      | μs   |

| 18               | tstahd,<br>Hold time (repeated) START condition. After this<br>period, the first clock pulse is generated. | 0.6  |      |      | μs   |

| 19               | tscllow,<br>LOW period of SCL clock                                                                        | 1.3  |      |      | μs   |

| 20               | tsclнigн,<br>HIGH period of SCL clock                                                                      | 0.6  |      |      | μs   |

| 21               | tstasu,<br>Setup time for a repeated START condition                                                       | 0.6  |      |      | μs   |

| 22               | tsdahd,<br>SDA data hold time                                                                              | 0    |      | 0.9  | μs   |

| 23               | tsdasu,<br>SDA data setup time                                                                             | 100  |      |      | ns   |

| 24               | tsтоsu,<br>Setup time for STOP condition                                                                   | 0.6  |      |      | μs   |

# **Control Register Definitions**

### 1. Notation

Addresses and constant values are defined using decimal or hexadecimal numbers. Where they are used, hexadecimal numbers are prepended with "0x".

Register definitions are given in the following format:

| ADDRESS |   |   | CESS MODE |   | CORE<br>DEFAULT VALUE |   |   |  |

|---------|---|---|-----------|---|-----------------------|---|---|--|

| 7       | 6 | 5 | 4         | 3 | 2                     | 1 | 0 |  |

|         |   |   |           |   |                       |   |   |  |

# Where,

REGISTERNAME: Name of the register (e.g. EQUCONFIG)

ACCESS MODE: Read (R), Write (W) or Read/Write (RW)

CORE: Which register group it belongs to.

ADDRESS: I<sup>2</sup>C bus address used to access register

DEFAULT VALUE: Value after chip reset or software equivalent

The most significant bit of each field is positioned to the left.

Where logical registers occupy more than a single 8-bit physical register (for example where a parameter field requires more than 8 bits of precision) they are defined together and allocated successive (byte) addresses.

#### 2. Number Format

Numerical values which can be positive or negative, use 2's complement number format. Numerical values which can be only positive, use plain unsigned binary representation.

SONY CXD1958Q

# 3. Register Definitions

# 3-1. TSMSTATUS

TSMSTATUS READ CORE

ADDRESS: 0x03 DEFAULT: 0x00

| 7          | 7 6 5 |      | 4     | 3 | 2          | 1 | 0 |

|------------|-------|------|-------|---|------------|---|---|

| AGC locked |       | Rese | erved |   | TSM status |   |   |

Bits 3 to 0: Current state of pre-processor state machine coded as follows:

| TSM status | Synchronization state     | State identifier |  |  |

|------------|---------------------------|------------------|--|--|

| 0          | Cold reset                | RST              |  |  |

| 1          | Initialize                | INI              |  |  |

| 2          | Coarse timing acquisition | CTA              |  |  |

| 3          | Fine timing acquisition A | FTA              |  |  |

| 4          | Fine timing acquisition B | FTB              |  |  |

| 5          | Tracking                  | TRK              |  |  |

| 6          | Pre-processor lost lock   | PLL              |  |  |

Bits 3 to 6: Reserved

Bit 7: Set by the pre-processor when the AGC is in lock. Refer to the description of registers

AGCTGT and AGCLKTHR.

# 3-2. ESMSTATUS

| ESMSTATUS<br>ADDRESS: 0 |      | RE    | AD | CORE<br>DEFAULT: 0x00 |  |  |  |  |  |

|-------------------------|------|-------|----|-----------------------|--|--|--|--|--|

| 7                       | 6    | 5     | 4  | 3 2 1 0               |  |  |  |  |  |

|                         | Rese | erved |    | ESM status            |  |  |  |  |  |

Bits 3 to 0: Current state of equalizer state machine coded as follows:

| ESM status | Synchronisation state          | State identifier |

|------------|--------------------------------|------------------|

| 0          | Reset                          | RESET            |

| 1          | Wait for Pre-processor to Lock | WPL              |

| 2          | Fine Gain Adjustment           | FGA              |

| 3          | Blind Linear Equalisation (1)  | BLE1             |

| 4          | Blind Linear Equalisation (2)  | BLE2             |

| 5          | Carrier Frequency Recovery     | CFR              |

| 6          | DC Correction                  | DCC              |

| 7          | Blind DFE Equalisation         | BDE              |

| 8          | S&G DFE Equalisation           | SDE              |

| 9          | DD DFE Equalisation            | DDE              |

| 10         | Check Spectral Inversion       | CSI              |

| 11         | Tracking                       | TRK              |

| 12         | Equalizer Lost Lock            | ELL              |

Bits 4 to 7: Reserved

# 3-3. QAMCONFIG

QAMCONFIG READ/WRITE CORE

ADDRESS: 0x06 DEFAULT : 0x84

| 7                  | 7 6 5 |       | 4                 | 3                 | 2                | 1                | 0                |

|--------------------|-------|-------|-------------------|-------------------|------------------|------------------|------------------|

| 256 QAM<br>Mapping | Rese  | erved | 256 QAM<br>Enable | 128 QAM<br>Enable | 64 QAM<br>Enable | 32 QAM<br>Enable | 16 QAM<br>Enable |

Bits 0 to 4: Clear appropriate bit to prevent the demodulator from attempting to synchronize with the

specified QAM. The default value is such that lock is only attempted with 64 QAM. If more than one QAM level is specified the equalizer attempts lock at each of the specified QAM levels until lock is achieved. This increases the lock time compared to setting the QAM level

if known.

Bits 5 to 6: Reserved

Bit 7: Clear this bit to use the DVB 256 QAM mapping. The default value of 1 means that, in 256

QAM mode, the MMDS mapping is used.

## 3-4. CARRIEROFFSET

| FREQOFFSET ADDRESS: 0x07 |                         |   | AD |   |   | CORE<br>DEFAULT: 0x00 |   |  |  |  |

|--------------------------|-------------------------|---|----|---|---|-----------------------|---|--|--|--|

| 7                        | 6                       | 5 | 4  | 3 | 2 | 1                     | 0 |  |  |  |

|                          | Detected Carrier Offset |   |    |   |   |                       |   |  |  |  |

Bits 0 to 7: Holds the detected coarse carrier frequency offset. This is a combination of any frequency offset correction applied in the pre-processor to allow symbol timing lock and the carrier frequency offset detected by the carrier recovery loop in the equalizer. It is encoded as follows:

Foff = CarrierOffset

$$\cdot \frac{Fs}{256}$$

Where Foff is the frequency offset from the nominal IF (or alias) and Fs is the ADC sample rate (nominally 30MHz). The maximum carrier frequency offset that can be accommodated is currently fixed at 512kHz although there may be SNR degradation for large offsets depending on the SAW filter used.

# 3-5. DETECTEDQAM

| DETECTEDQ<br>ADDRESS: 0 |   | RE       | AD |   | CORE<br>DEFA       |   |   |

|-------------------------|---|----------|----|---|--------------------|---|---|

| 7                       | 6 | 5        | 4  | 3 | 2                  | 1 | 0 |

|                         |   | Reserved |    |   | Detected QAM Level |   |   |

Bits 0 to 3: Once the equalizer has lock this register contains the QAM level for which the equalizer locked and is decoded as follows:

| Register value | QAM level |  |  |  |  |  |

|----------------|-----------|--|--|--|--|--|

| 0              | 16        |  |  |  |  |  |

| 1              | 32        |  |  |  |  |  |

| 2              | 64        |  |  |  |  |  |

| 3              | 128       |  |  |  |  |  |

| 4              | 256       |  |  |  |  |  |

Bits 3 to 7: Reserved

### 3-6. DETECTEDSYMRATE

| ADDRESS: 0x09 to 0A |          |   |   |            | READ |   |   |            | CORE<br>DEFAULT: 0x0 |   |   |   |   |   |   |   |

|---------------------|----------|---|---|------------|------|---|---|------------|----------------------|---|---|---|---|---|---|---|

|                     | 7        | 6 | 5 | 4          | 3    | 2 | 1 | 0          | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                     | Reserved |   |   | TrialSRate |      |   |   | TrialSRate |                      |   |   |   |   |   |   |   |

Bits 0 to 3 & 0 to 7: Holds the last symbol rate at which the timing recovery PLL locked and which subsequently lead to valid MPEG packets being decoded by the FEC block. This symbol rate is restored as the trial symbol rate when the demodulator performs a hot reset and is encoded as follows:

$$SymbolRate = \frac{TrialSRate}{16384} \cdot Fs$$

Where Fs is the ADC sample rate (nominally 30MHz).

SONY CXD1958Q

#### 3-7. PRECONFIG

PRECONFIG READ/WRITE CORE

ADDRESS: 0x11 DEFAULT: 0x89

| 7                  | 6 | 5        | 4 | 3                    | 2               | 1        | 0         |

|--------------------|---|----------|---|----------------------|-----------------|----------|-----------|

| Discrete<br>Search |   | Reserved |   | ADC Offset<br>Binary | ADC<br>External | AGC Hold | Hot Reset |

Bit 0: When set this enables a hot reset when the FEC block indicates that it has lost sync. This

causes the pre-processor state machine to resume operation at a point where it can exploit

prior knowledge of the received signal format gained whilst the chip was in lock.

Specifically, a hot reset causes the PSM to restore values for IF carrier frequency offset and symbol rate used when the FEC last indicated that valid MPEG code words were being received. This facility is provided to minimize the time required for re-acquisition of sync in applications using a single symbol rate and can only be invoked from the state where the

demodulator once had lock and subsequently lost it.

Bit 1: Set to hold the AGC output at its current value following a warm reset rather than being

reset to mid-range. This may reduce AGC acquisition times following a channel switch if

signal levels are similar.

Bit 2: Set to select the output of an external A/D converter for connection to the pre-processor

instead of the (default) internal A/D.

Bit 3: The signal processing elements of the pre-processor assume 2's complement data is being

supplied. Setting this bit inverts the top bit of the ADC output, converting the data format

from offset binary to 2's complement.

Bits 4 to 6: Reserved

Bit 7: Set to enable a symbol rate search at the discrete frequencies specified in the table

SYMBRATETRIAL0 – SYMBRATETRIAL7. In this mode, the pre-processor attempts to recover symbol synchronization at the specified symbol rates only. If lock is not achieved within the time limit specified by CTATIMEOUT acquisition is attempted at the next

frequency.

SONY CXD1958Q

### 3-8. AGCCTRL

AGCCTL READ/WRITE CORE

ADDRESS: 0x12 DEFAULT: 0x00

| 7 | 6 | 5        | 4 | 3 | 2          | 1        | 0          |

|---|---|----------|---|---|------------|----------|------------|

|   |   | Reserved |   |   | Invert AGC | AGC Time | e Constant |

Bits 0 to 1: This controls the time constant of the AGC loop. The hardware reset value of 0 disables the

AGC. A nominal setting of 2 should be programmed following power-up. This will allow the PWM average output to slew from its mid-range value to full scale in approximately 11ms. A setting of 1 doubles the time constant to 22ms and 3 halves it. A subsequent setting of 0 locks the AGC output at its current level. The AGC control loop will be disabled at power-up with the AGC output pin giving a 50% duty cycle output. The host microprocessor should set the correct sense for the control loop and enable the AGC by setting AGC\_TC to 2. A

subsequent warm or cold reset will not reset either of these parameters.

Bit 2: This controls the sense of the AGC loop. The default value of "0" will give a decreasing control output when the input is overloaded. A value of "1" will give an increasing value.

## 3-9. EQUCONFIG

EQUCONFIG READ/WRITE CORE

ADDRESS: 0x13 DEFAULT: 0x03

| 7 | 6 | 5        | 4 | 3 | 2                  | 1           | 0         |

|---|---|----------|---|---|--------------------|-------------|-----------|

|   |   | Reserved |   |   | Invert<br>Spectrum | Disable CSI | Hot Reset |

Bit 0: When set this enables a hot reset when the FEC block indicates that it has lost lock. This

causes the equalizer state machine to resume operation at a point where it can exploit prior knowledge of the received signal format gained whilst the chip was in lock. Specifically, a hot reset causes the ESM to restore the last values for QAM order and spectral inversion

used before the FEC indicated loss of lock.

Bit 1: The device will automatically toggle the input spectrum once the equalizer has locked if the

FEC has not locked. This toggling feature can be disabled by setting this bit.

Bit 2: Set this to invert the spectrum of the input signal. It is not inverted by default. The setting of

this bit is dependent upon the frequency plan used in the tuner.

Bits 3 to 7: Reserved

#### 3-10. SYMRATETRIALO

**SYMRATETRIALO READ/WRITE** CORE ADDRESS: 0x15 & 0x16 **DEFAULT: 0xAAB** 7 7 2 1 0 5 1 0 6 6 Trial Symbol Rate 0 Trial Symbol Rate 0 Reserved

Bits 0 to 7 & 0 to 3: The SYMRATETRIAL0 – SYMRATETRIAL7 registers control the frequencies at which the timing loop attempts to lock. Their function depends upon the setting of the discrete search bit (bit 7) in the PRECONFIG register.

When disabled (i.e. set to zero) the pre-processor performs a continuous symbol rate search which extends from the frequency specified in SYMRATETRIAL0 down to that specified in SYMRATETRIAL1. The search must be performed downwards in frequency and so SYMRATETRIAL0 defines the high frequency limit of the search range. When discrete search is enabled (i.e. set to one) the pre-processor attempts to synchronize at each of up to 8 discrete frequencies specified in SYMRATETRIAL0 – SYMRATETRIAL7. In this case SYMRATETRIAL0 defines the first symbol rate to test. If a discrete rate is set to zero then this causes the search to reset to TRIAL0 and start again. Therefore if a known single symbol rate is used then SYMRATETRIAL0 should be set appropriately and SYMRATETRIAL1 should be set to zero.

For both modes the register setting is given by:

$$SYMRATETRIAL0 = \frac{Fsym}{Fs} \cdot 16384$$

Where Fsym is the symbol rate and Fs is the ADC sample rate (nominally 30MHz). The default value of 2731 corresponds to 5Msym/s with a 30MHz sample clock.

#### 3-11. SYMRATETRIAL1

SYMRATETRIAL1 **READ/WRITE** CORE ADDRESS: 0x17 & 0x18 **DEFAULT: 0x0** 7 3 7 2 6 5 4 2 1 0 6 5 4 3 1 0 Trial Symbol Rate 1 Reserved Trial Symbol Rate 1

• See SYMRATETRIAL0 register description.

# 3-12. SYMRATETRIAL2

SYMRATETRIAL2 READ/WRITE CORE

ADDRESS: 0x19 & 0x1A DEFAULT: 0x0

| 7 | 6    | 5     | 4 | 3    | 2       | 1       | 0   | 7 | 6 | 5   | 4      | 3       | 2    | 1 | 0 |

|---|------|-------|---|------|---------|---------|-----|---|---|-----|--------|---------|------|---|---|

|   | Rese | erved |   | Tria | al Syml | ool Rat | e 2 |   |   | Tri | al Sym | bol Rat | te 2 |   |   |

• See SYMRATETRIAL0 register description.

### 3-13. SYMRATETRIAL3

SYMRATETRIAL3 READ/WRITE CORE

ADDRESS: 0x1B & 0x1C DEFAULT: 0x0

| 7 | 6    | 5     | 4 | 3    | 2       | 1       | 0   | 7 | 6 | 5   | 4      | 3       | 2   | 1 | 0 |

|---|------|-------|---|------|---------|---------|-----|---|---|-----|--------|---------|-----|---|---|

|   | Rese | erved |   | Tria | al Syml | ool Rat | e 3 |   |   | Tri | al Sym | bol Rat | e 3 |   |   |

<sup>•</sup> See SYMRATETRIALO register description.

# 3-14. SYMRATETRIAL4

SYMRATETRIAL4 READ/WRITE CORE

ADDRESS: 0x1D & 0x1E DEFAULT: 0x0

| 7        | 6 | 5 | 4 | 3    | 2       | 1       | 0   | 7 | 6 | 5   | 4      | 3       | 2    | 1 | 0 |

|----------|---|---|---|------|---------|---------|-----|---|---|-----|--------|---------|------|---|---|

| Reserved |   |   |   | Tria | al Syml | ool Rat | e 4 |   |   | Tri | al Sym | bol Rat | te 4 |   |   |

<sup>•</sup> See SYMRATETRIALO register description.

# 3-15. SYMRATETRIAL5

SYMRATETRIAL5 READ/WRITE CORE

ADDRESS: 0x1F & 0x20 DEFAULT: 0x0

| 7 | 6    | 5     | 4 | 3    | 2       | 1       | 0   | 7 | 6 | 5   | 4      | 3       | 2   | 1 | 0 |

|---|------|-------|---|------|---------|---------|-----|---|---|-----|--------|---------|-----|---|---|

|   | Rese | erved |   | Tria | al Syml | ool Rat | e 5 |   |   | Tri | al Sym | bol Rat | e 5 |   |   |

<sup>•</sup> See SYMRATETRIALO register description.

CXD1958Q

### 3-16. SYMRATETRIAL6

SYMRATETRIAL6 READ/WRITE CORE

ADDRESS: 0x21 & 0x22 DEFAULT: 0x0

| 7 | 6    | 5     | 4 | 3    | 2       | 1       | 0   | 7 | 6 | 5   | 4      | 3       | 2    | 1 | 0 |

|---|------|-------|---|------|---------|---------|-----|---|---|-----|--------|---------|------|---|---|

|   | Rese | erved |   | Tria | al Syml | ool Rat | e 6 |   |   | Tri | al Sym | bol Rat | te 6 |   |   |

<sup>•</sup> See SYMRATETRIALO register description.

## 3-17. SYMRATETRIAL7

SYMRATETRIAL7 READ/WRITE CORE

ADDRESS: 0x23 & 0x24 DEFAULT: 0x0

| 7 | 6    | 5     | 4 | 3    | 2       | 1       | 0   | 7 | 6 | 5   | 4      | 3       | 2   | 1 | 0 |

|---|------|-------|---|------|---------|---------|-----|---|---|-----|--------|---------|-----|---|---|

|   | Rese | erved |   | Tria | al Syml | ool Rat | e 7 |   |   | Tri | al Sym | bol Rat | e 7 |   |   |

<sup>•</sup> See SYMRATETRIALO register description.

#### **3-18. ITBFREQ**

ITBFREQ READ/WRITE CORE

ADDRESS: 0x29 & 0x2A DEFAULT: 0x32EF

| 7    | 6     | 5   | 4      | 3      | 2       | 1      | 0  | 7 | 6  | 5     | 4      | 3       | 2      | 1  | 0 |

|------|-------|-----|--------|--------|---------|--------|----|---|----|-------|--------|---------|--------|----|---|

| Rese | erved | ITI | B Dowr | nconve | rsion F | requen | су |   | ΙΤ | B Dow | nconve | rsion F | requer | су |   |

Bits 0 to 5 & 0 to 7: Nominal frequency of the receive local oscillator, encoded as follows:

ITBFREQ =

$$-16384 \cdot \frac{Fc}{Fs}$$

Where Fc is the centre frequency of the IF (or alias) and Fs is the ADC sample rate (nominally 30MHz). The setting of a negative value for ITBFREQ implies no spectrum inversion, whereas a positive value inverts the spectrum. This register sets the nominal received local oscillator frequency. Any frequency offsets are recovered separately within the device and fed back to the local oscillator.

The default value of –3345 corresponds to a nominal frequency of 36.125MHz which aliases to 6.125MHz.

SONY CXD1958Q

#### 3-19. EQUTAPSELECT

TAPSELECT

READ/WRITE

CORE

ADDRESS: 0x2B

DEFAULT: 0x00

7

6

5

4

3

2

1

0

Reserved

Tap Select

Bits 0 to 5: Set this register to select tap number whose values are loaded into the TAPI and TAPQ

registers. The feedforward taps are numbered 0 to 9 with the main tap being tap 9. The

feedback taps are numbered 10 to 39 with 10 being the first feedback tap.

Bits 6, 7: Reserved

# **3-20. EQUTAPI**

| TAPREAL<br>ADDRESS: 0 | x2C | RE | AD |         | CORE<br>DEFA | ULT: 0x00 |  |  |  |  |  |

|-----------------------|-----|----|----|---------|--------------|-----------|--|--|--|--|--|

| 7                     | 6   | 5  | 4  | 3 2 1 0 |              |           |  |  |  |  |  |

| Tap value (in-phase)  |     |    |    |         |              |           |  |  |  |  |  |

Bits 0 to 7: Contains the real (in-phase) component of the equalizer tap specified by the TAPSELECT register. This must be read before the EQUTAPQ register.

## **3-21. EQUTAPQ**

| TAPQUAD<br>ADDRESS: 0 | x2D | RE          | AD        |            | CORE<br>DEFA | ULT: 0x00 |  |  |  |

|-----------------------|-----|-------------|-----------|------------|--------------|-----------|--|--|--|

| 7                     | 6   | 5 4 3 2 1 0 |           |            |              |           |  |  |  |

|                       |     |             | Tap value | (in-phase) |              |           |  |  |  |

Bits 0 to 7: Contains the imaginary (quadrature-phase) component of the equalizer tap specified by the TAPSELECT register. The process of reading this register automatically loads the next tap values into the EQUTAPI and EQUTAPQ registers (i.e. the TAPSELECT register need only be set once to obtain all the tap values).

SONY CXD1958Q

### 3-22. CONSTELLATIONI

| ADDRESS: 0x2E |                                           |   | AD | CORE DEFAULT: 0x00  3 2 1 0 |  |  |  |  |  |

|---------------|-------------------------------------------|---|----|-----------------------------|--|--|--|--|--|

| 7             | 6                                         | 5 | 4  | 3 2 1 0                     |  |  |  |  |  |

|               | Equalizer Constellation Output (In-phase) |   |    |                             |  |  |  |  |  |

Bbus its 0 to 7: Contains the real (in-phase) component of the equalizer output before the decision device.

Due to the speed limitations of the I<sup>2</sup>C bus this data is not continuous but is a sub-sampled version of the equalizer output. Even so, because of the random nature of the data, a constellation plot can still be formed from this data.

# 3-23. CONSTELLATIONQ

| CONSTELLATIONQ F ADDRESS: 0x2F                    |   |   | AD |   | CORE<br>DEFA | ULT: 0x00 |  |  |

|---------------------------------------------------|---|---|----|---|--------------|-----------|--|--|